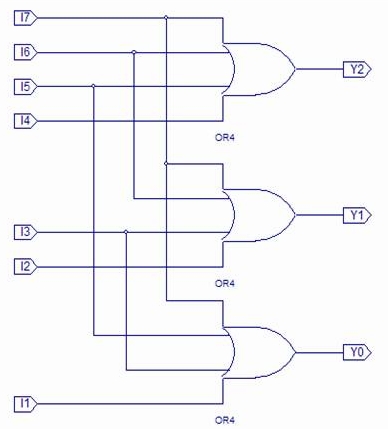

1. 下图为普通的 8线-3线 编码器,其输入输出的真值表如 表1 所示。 【下载案例】 【更多案例】

表1. 8 线 -3 线编码器的真值表 | |

I0 I1 I2 I3 I4 I5 I6 I7 | Y2Y1Y0 |

1 0 0 0 0 0 0 0 | 0 0 0 |

0 1 0 0 0 0 0 0 | 0 0 1 |

0 0 1 0 0 0 0 0 | 0 1 0 |

0 0 0 1 0 0 0 0 | 0 1 1 |

0 0 0 0 1 0 0 0 | 1 0 0 |

0 0 0 0 0 1 0 0 | 1 0 1 |

0 0 0 0 0 0 1 0 | 1 1 0 |

0 0 0 0 0 0 0 1 | 1 1 1 |

2. 实验内容及步骤

1) 新建一个工程 Test_1 。

2) 新建 3 线 -8 线编码器的原理图文件 CODE8_3.SCH ,按图 1.1 输入原理图,生成编码器模块 Code8_3 。

3) 新建测试激励文件 Code8_3_T.Twb, 按照表 1.1 设置输入。

4) 仿真,记录实验数据 , 并与真值表对照。

5) 定义引脚,下载验证。

定义模块的各输入输出端口,并下载到硬件板运行,观察实际效果。